21+ How To Pipeline Verilog

Using verilog and ModelSim to build a pipeline CPU PipeRegsv defines the regs between each stage of the pipeline CPU. Web When we shift the mcand to the left by 8 bits we make the least 8 significant bits in the partial product zero which is what I would expect but we also lose the 8 most significant bits of the mcand.

Pdf Verilog Implementation Of A Mips Risc 32 Bit Pipelined Processor Architecture Semantic Scholar

A Practical Primer httpamzn.

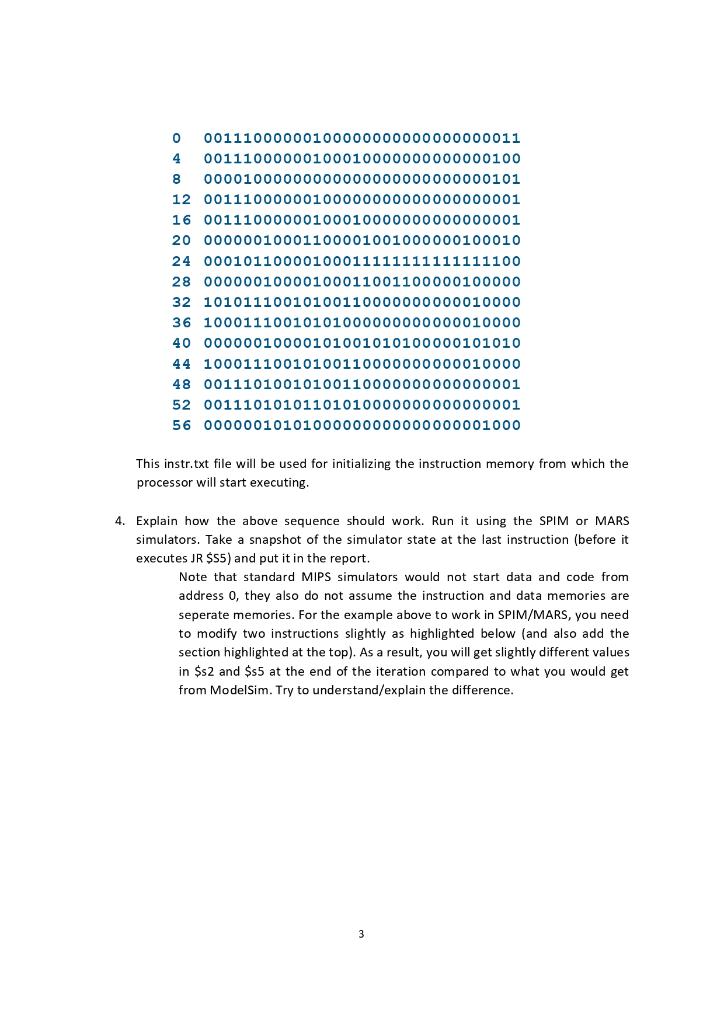

. Web March 15 2021 at 741 AM Verilog. Instruction fetch IF instruction decode ID execution EX memory access and write. Web MIT - Massachusetts Institute of Technology.

My platform is a Zynq 7010-based. Web In Back-end Flow after synthesis of any design when our design is changed into gates level design we place our gatesflops or other cells according to our power and. Web Pipelined MIPS Processor in Verilog Part-3 This project is to present the Verilog code for a 32-bit pipelined MIPS Processor.

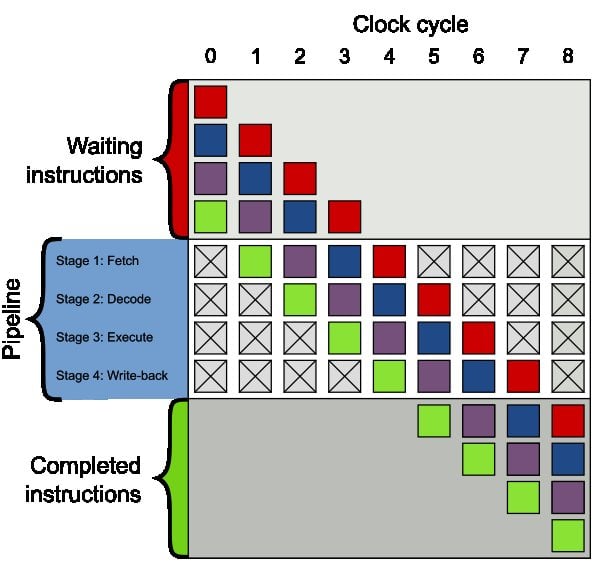

Web Pipeline design is to divide the path system into digital processing units stage And a register is inserted between each processing unit to temporarily store the data of the. In part 2 I presented all the Verilog code for the. How to implement a pipeline multiplier.

Five stages of a microprocessor. For n-level pipeline system in the case of conditional jump you need to flush pipline queue provide. Hey Id like to implement a 31 32-bit signed multiplier using Verilog.

Web Like the video and Subscribe to channel if you liked the videoRecommended BooksAmazon books Links Verilog Hdl Synthesis. I think that problem is not so easy. Web Checkout the complete pipeline operation and space time table.

In paper and pencil multiplication we normally keep all the bits of the mcand and simply add 8 zeros to the end. User11036132 Jun 9 2019 at 1333. It requires more registers than you would.

So with pipeline we can implement hardware efficiently. Web verilog pipelined With Xilinx FPGA such as Spartan-3 and Virtex-II you must be extra careful when pipelining multipliers. Web A classic 5-stage pipeline MIPS 32-bit processor.

To calculate speed up in execution time follow following.

Pipelined Mips Processor In Verilog Part 2 Fpga4student Com

Verilog Code For 16 Bit Mips Pipelined Processor Shashi Suman

Verilog Code For 16 Bit Risc Processor Fpga4student Com

The Why And How Of Pipelining In Fpgas Technical Articles

Verilog Code For 16 Bit Risc Processor Fpga4student Com

Assignment 3 A Tacky Pipeline

Rtl Verilog For Parallel Execution Of 3 Stage Pipeline Download Scientific Diagram

Risc V Microprocessor Using Tl Verilog In 5 Days By Shivani Shah Medium

Shows A Block Diagram For A Simple Sequential Pipeline Register Download Scientific Diagram

Pipeline Adder Verilog Code Verilog Implementation Of 16 Bit Pipeline Adder

Pipelined Mips Processor In Verilog Part 1 Fpga4student Com

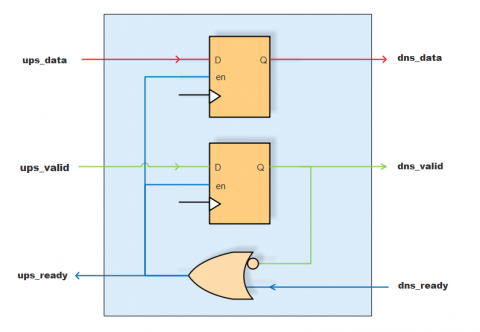

Pipelining Axi Buses With Registered Ready Signals Itdev

Part 1 50 For The Pips Pipeline Verilog Chegg Com

Rtl Verilog For Parallel Execution Of 3 Stage Pipeline Download Scientific Diagram

Coding Consideration For Pipeline Flip Flops Edn Asia

Rtl Verilog For Parallel Execution Of 3 Stage Pipeline Download Scientific Diagram

The Why And How Of Pipelining In Fpgas Technical Articles